## NATIONAL UNIVERSITY OF IRELAND, GALWAY

#### DOCTORAL THESIS

## IMPAIR: Massively Parallel Regularised Richardson-Lucy Image Deconvolution on Heterogeneous Hardware

Author:

Michael Sherry

Supervisor:

Prof. Andy Shearer

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

in the

Centre for Astronomy School of Physics

October 2017

# Contents

| $\mathbf{C}$  | onten  | uts                                                                    | i    |

|---------------|--------|------------------------------------------------------------------------|------|

| Li            | st of  | Figures                                                                | vii  |

| $\mathbf{Li}$ | st of  | Tables                                                                 | ix   |

| $\mathbf{A}$  | bstra  | ${f ct}$                                                               | xi   |

| $\mathbf{A}$  | cknov  | wledgements                                                            | xi   |

| D             | eclara | ation of Authorship                                                    | xiii |

| 1             | Het    | erogeneous Computing on the Modern Desktop Computer                    | 1    |

|               | 1.1    | Introduction                                                           | 1    |

|               | 1.2    | Concurrency and Parallelism                                            | 2    |

|               | 1.3    | The Flynn Taxonomy                                                     | 3    |

|               | 1.4    | Parallelism in the Modern Desktop Computer                             | 10   |

|               | 1.5    | Synchronisation & Lockstep Execution                                   | 12   |

|               | 1.6    | Parallel Speedup                                                       | 13   |

|               | 1.7    | Parallel Slowdown                                                      | 14   |

|               | 1.8    | This Work                                                              | 16   |

| 2             | Ima    | ge Processing                                                          | 19   |

|               | 2.1    | Introduction                                                           | 19   |

|               | 2.2    | Computer Vision, The Image Processing Pipeline & The Semantic Gap $$ . | 19   |

|               | 2.3    | Image Restoration                                                      | 21   |

|               | 2.4    | Metrics of Image Quality                                               | 21   |

|               | 2.5    | Denoising                                                              | 22   |

|               | 2.6    | Deconvolution & The Deconvolution Problem                              | 23   |

|               | 2.7    | The Zoo of Deconvolution Algorithms                                    | 24   |

|               | 2.8    | Richardson-Lucy Deconvolution                                          | 26   |

|               | 2.9    | Noise Amplification Problem                                            | 27   |

|               | 2.10   | Spatially Variant Richardson-Lucy Deconvolution                        | 29   |

|               | 2.11   | Regularised Richardson-Lucy Deconvolution                              | 29   |

|               | 2.12   | PSF recovery and Blind Deconvolution                                   | 30   |

|               | 2.13   | Related Work                                                           | 31   |

|               |        | 2.13.1 The Discrete Wavelet Transform                                  | 32   |

|               |        | 2.13.2 Deconvolution                                                   | 33   |

|   | 2.14              | Conclusion                                                                                                                        | . 34  |

|---|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|

| 3 | 3.1               | PAIR Introduction                                                                                                                 |       |

|   | 3.2               | Convolution of 1D, 2D, and 3D Signal Data                                                                                         |       |

|   | 3.3               | Discrete Convolution in the spatial domain                                                                                        |       |

|   | 3.4               | Discrete Convolution in the frequency domain                                                                                      |       |

|   | 3.5               | Discrete Convolution defined recursively                                                                                          |       |

|   | $\frac{3.6}{3.7}$ | Overlap Sava Image Tiling                                                                                                         |       |

|   | 3.8               | Overlap-Save Image Tiling                                                                                                         |       |

|   | 3.9               | Richardson Lucy Algorithms                                                                                                        |       |

|   |                   | Parallel RL for cluster-based computing                                                                                           |       |

|   | 0.10              | 3.10.1 Richardson Lucy Border Conditions                                                                                          |       |

|   |                   | 3.10.2 Parallelising The Blind Richardson-Lucy Algorithm                                                                          |       |

| 4 | The               | Wavelet Transform Library for the GPU and CPU                                                                                     | 51    |

|   | 4.1               | Wavelet Regularised Richardson Lucy                                                                                               | . 51  |

|   | 4.2               | Daubechie Wavelets                                                                                                                | . 51  |

|   | 4.3               | Algorithm Overview                                                                                                                | . 52  |

|   | 4.4               | Parallelisation Strategies                                                                                                        | . 55  |

|   | 4.5               | DWT Benchmarks                                                                                                                    |       |

|   | 4.6               | Wavelet Shrinking Benchmarks                                                                                                      |       |

|   | 4.7               | Conclusion                                                                                                                        | . 66  |

| 5 |                   | Richardson-Lucy Deconvolution Library for the GPU and CPU                                                                         |       |

|   | 5.1               | Introduction                                                                                                                      |       |

|   | 5.2               | Image Restoration Performance                                                                                                     |       |

|   | 5.3               | IMPAIR Images                                                                                                                     |       |

|   | $5.4 \\ 5.5$      | Computational Performance                                                                                                         |       |

|   | 5.5               | 5.5.1 CPU Naive                                                                                                                   |       |

|   |                   | 5.5.2 CPU Topdown                                                                                                                 |       |

|   |                   | 5.5.3 CPU Streaming                                                                                                               |       |

|   |                   | 5.5.4 CPU Queuing                                                                                                                 |       |

|   | 5.6               | GPU IMPAIR Runtimes                                                                                                               |       |

|   |                   | 5.6.1 GPU Naive                                                                                                                   |       |

|   |                   | 5.6.2 GPU Streaming                                                                                                               |       |

|   | 5.7               | CPU-GPU Comparison                                                                                                                |       |

|   |                   | 5.7.1 Naive                                                                                                                       |       |

|   |                   | 5.7.2 GPU Streaming & CPU Topdown                                                                                                 | . 105 |

|   |                   | 5.7.3 GPU Streaming & CPU Streaming & CPU Queuing                                                                                 |       |

|   | 5.8               | Conclusion                                                                                                                        | . 109 |

| 6 | Ana               | lysis                                                                                                                             | 111   |

|   | 6.1               | $ Introduction \dots \dots$ | . 111 |

|   | 6.2               | Memory Footprint                                                                                                                  | . 111 |

|   | 6.3               | Memory Hierarchy                                                                                                                  | 11/   |

|              | 6.4   | Conclusion                                                                   | . 124     |

|--------------|-------|------------------------------------------------------------------------------|-----------|

| 7            |       | ure Directions: Towards a general, high-throughput, Blind Decoration library | n-<br>125 |

|              | 7.1   | GPU Queuing Strategy                                                         | . 125     |

|              | 7.2   | Implement a Simultaneous Forward and Inverse Wavelet Transform               | . 125     |

|              | 7.3   | Investigate Cache-Share penalty                                              | . 126     |

|              | 7.4   | Single and Multi-dimensional DWT & WRL                                       | . 126     |

|              | 7.5   | Additional Wavelet Shrinking Algorithms                                      | . 126     |

|              | 7.6   | Ports                                                                        | . 127     |

|              | 7.7   | Bindings                                                                     | . 127     |

|              | 7.8   | Runtime Profiles of Deconvolution for PSF Recovery                           | . 128     |

|              | 7.9   | Blind Deconvolution on the GPU and CPU                                       | . 128     |

| Δ            | TMI   | PAIR Deconvolution Library API                                               | 129       |

|              | A.1   | Use Cases                                                                    |           |

|              | A.2   | Implementations                                                              |           |

|              |       | Library API                                                                  |           |

|              | 11.0  | A.3.1 API Design                                                             |           |

|              |       | A.3.2 The IMPAIR Library Helper Functions and Datatypes                      |           |

|              |       | A.3.3 C Multicore API                                                        |           |

|              |       | A.3.4 C GPU API                                                              |           |

|              |       | A.3.5 C CUDA API                                                             |           |

| В            | IMI   | PAIR Discrete Wavelet Transform Library API                                  | 143       |

|              | B.1   | Use Cases                                                                    | . 143     |

|              | B.2   | API                                                                          | . 144     |

|              |       | B.2.1 The DWT Library Helper Functions and Datatypes                         | . 144     |

|              |       | B.2.2 The CPU Library                                                        | . 145     |

|              |       | B.2.3 The GPU Library                                                        | . 149     |

| $\mathbf{C}$ | App   | pendix C                                                                     | 153       |

| Bi           | bliog | graphy                                                                       | 155       |

# List of Figures

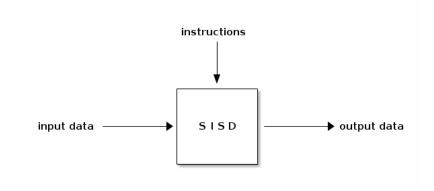

| 1.1  | Flynn's SISD Interface                                            | 4  |

|------|-------------------------------------------------------------------|----|

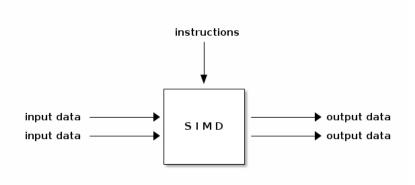

| 1.2  | Flynn's SIMD Interface                                            | 5  |

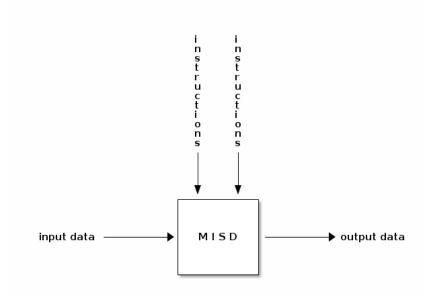

| 1.3  | Flynn's MISD Interface                                            | 6  |

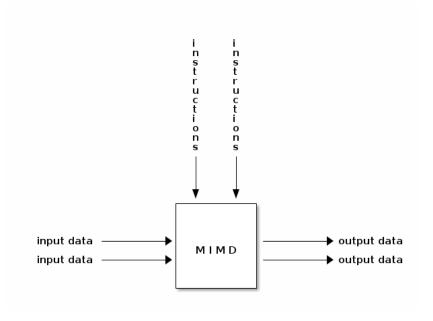

| 1.4  | Flynn's MIMD Interface                                            |    |

| 1.5  | Multicore CPU Design                                              | 11 |

| 2.1  | IMPAIR Inverse Filtering Example Images                           | 24 |

| 2.2  | IMPAIR Inverse Filtering Noise Amplification Example Images       | 24 |

| 2.3  | Image Sharpening $3 \times 3$ Pixel Kernel                        | 25 |

| 2.4  | Image Sharpening $5 \times 5$ Pixel Kernel                        | 25 |

| 2.5  | IMPAIR Noise Amplification Example Images                         | 28 |

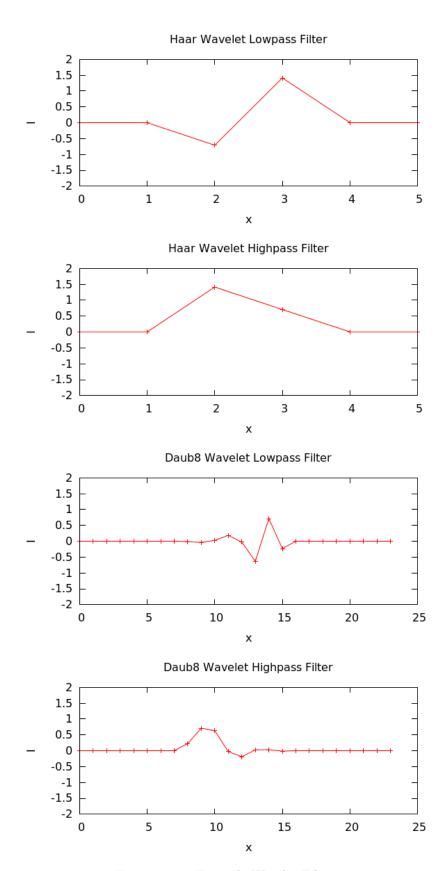

| 4.1  | Example Wavelet Filters                                           | 53 |

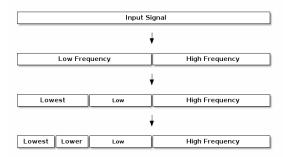

| 4.2  | The One Dimensional Discrete Wavelet Transform                    | 54 |

| 4.3  | The Two Dimensional Discrete Wavelet Transform                    | 54 |

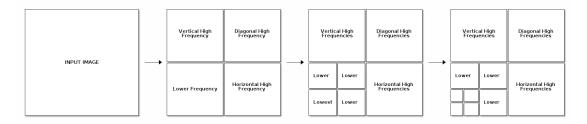

| 4.4  | Haar Megapixel Image Performances                                 | 58 |

| 4.5  | Daub-8 Megapixel Image Performances                               | 59 |

| 4.6  | DWT Per-Core Speedups                                             | 60 |

| 4.7  | GPU Megapixel Image Performances                                  | 61 |

| 4.8  | GPU and CPU Forward DWT Runtimes                                  | 62 |

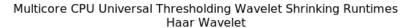

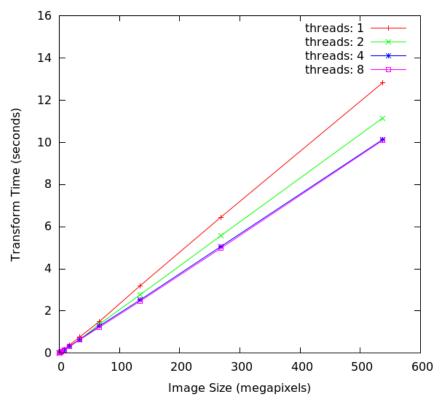

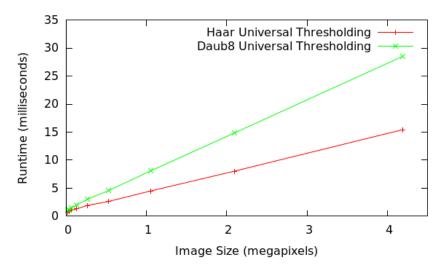

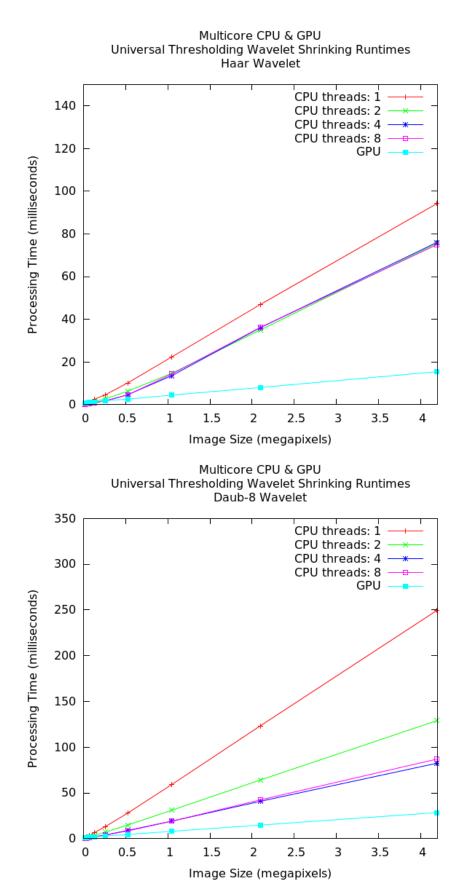

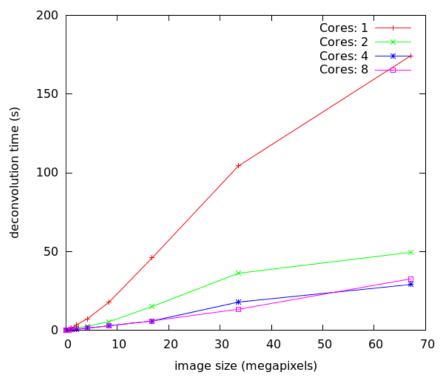

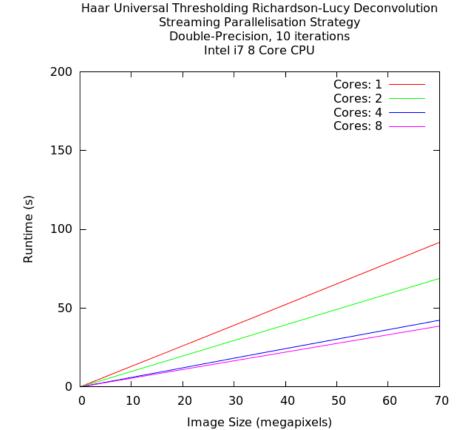

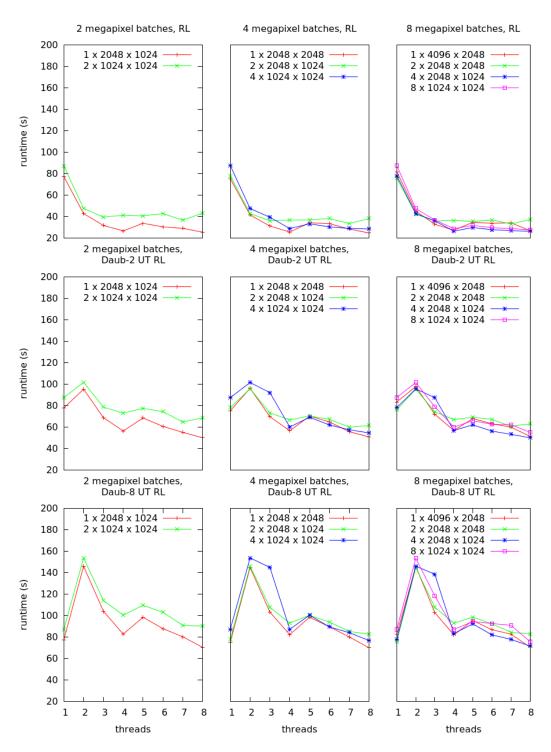

| 4.9  | Universal Thresholding Megapixel Image Performances               | 65 |

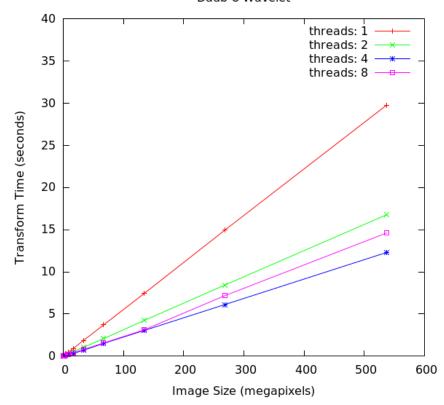

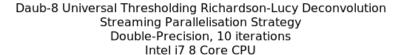

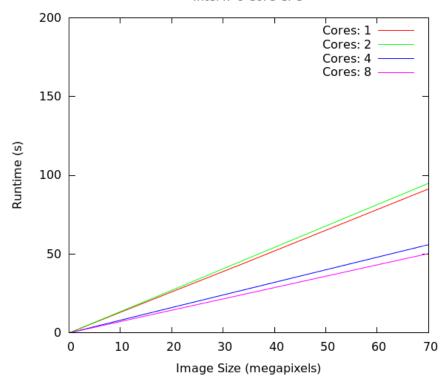

| 4.10 | Universal Thresholding Per-Core Speedups                          | 66 |

| 4.11 | GPU Universal Thresholding Megapixel Image Performances           | 67 |

| 4.12 | CPU-GPU Wavelet Shrinking Comparison                              | 68 |

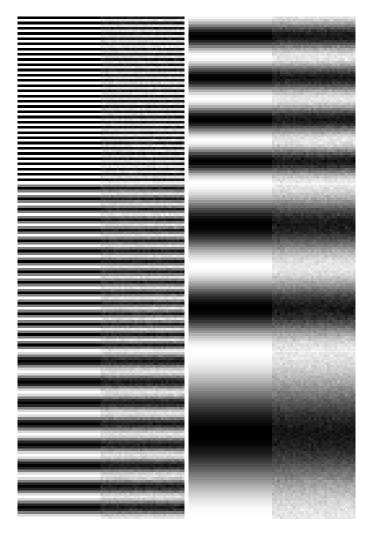

| 5.1  | Spatial Frequency Test Charts                                     | 71 |

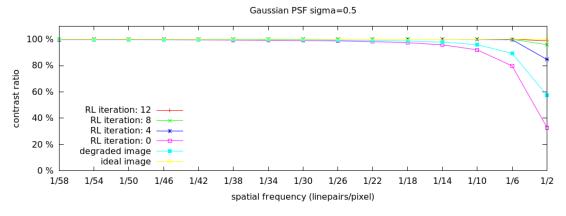

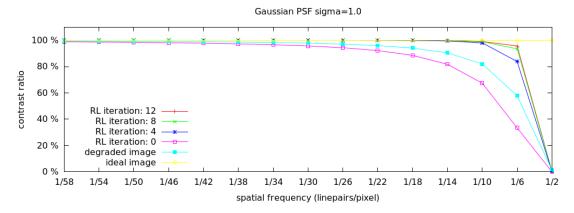

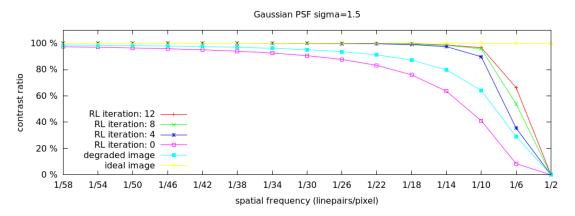

| 5.2  | Noiseless Image Restoration MTF Plot                              | 71 |

| 5.3  | Noiseless Image Restoration MTF Plot                              | 72 |

| 5.4  | Noiseless Image Restoration MTF Plot                              | 72 |

| 5.5  | Noisy Image Restoration MTF Plot                                  | 73 |

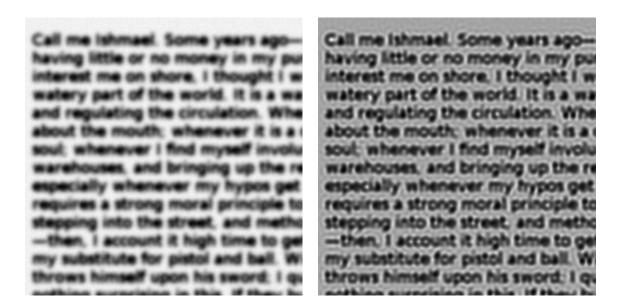

| 5.6  | Low Noise Restoration with Unregularised Richardson-Lucy          | 74 |

| 5.7  | High Noise Restoration with Unregularised Richardson-Lucy         | 75 |

| 5.8  | Unregularised Restoration with thinner PSF                        | 75 |

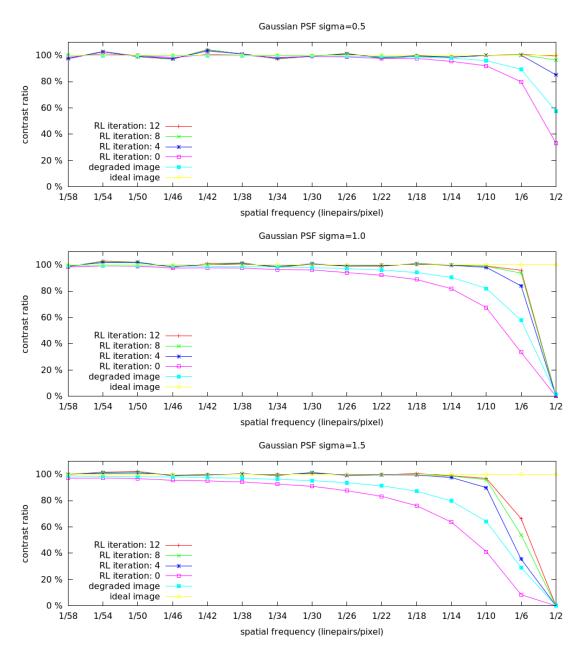

| 5.9  | Uncorrupted and Corrupted Example Images                          | 76 |

| 5.10 | Unregularised and Wavelet-Regularised Richardson-Lucy Restoration | 76 |

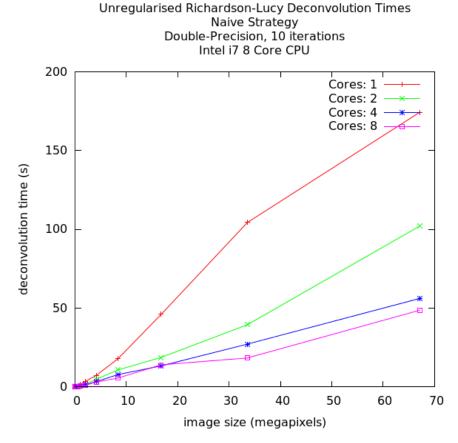

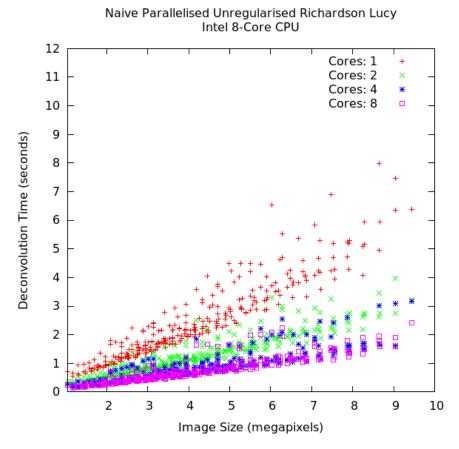

| 5.11 | Unregularised Naive Megapixel Image Performance                   | 79 |

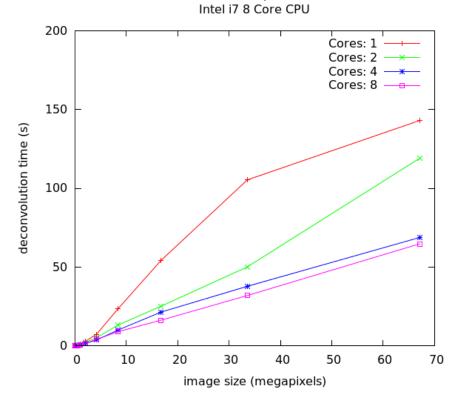

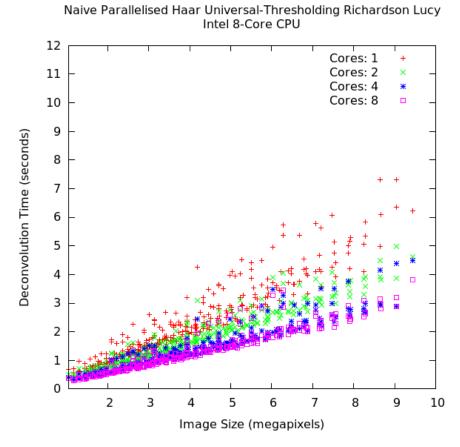

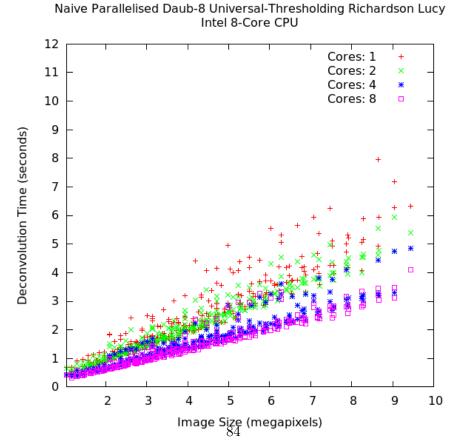

|      | Regularised Naive Megapixel Image Performance                     | 80 |

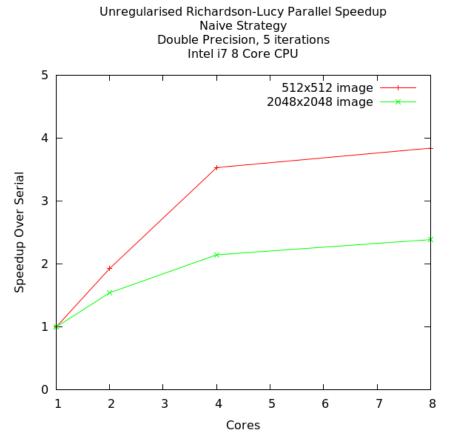

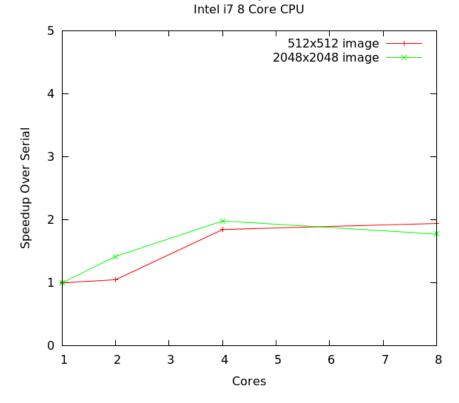

| 5.13 | Unregularised Naive Per-Core Speedups                             | 81 |

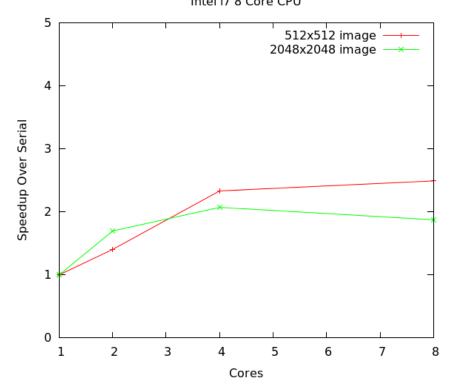

| 5.14 | Regularised Naive Per-Core Speedups                                                    |

|------|----------------------------------------------------------------------------------------|

| 5.15 | Unregularised Naive Runtime Variations                                                 |

| 5.16 | Haar Universal Thresholding Naive Runtime Variations                                   |

| 5.17 | Daub-8 Universal Thresholding Naive Runtime Variations 84                              |

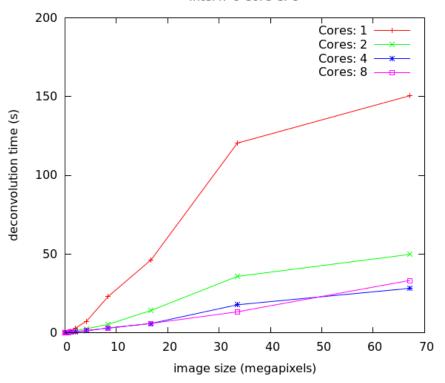

| 5.18 | Unregularised Topdown Megapixel Image Performance                                      |

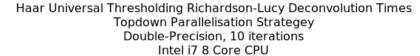

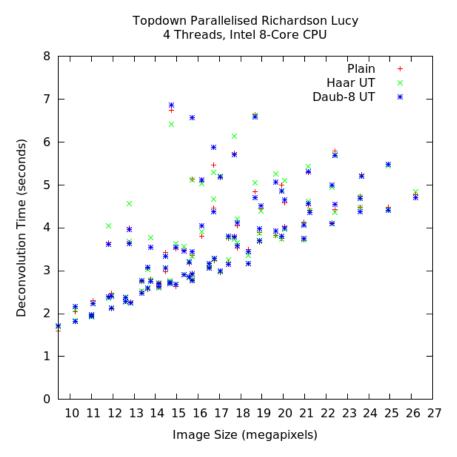

| 5.19 | Regularised Topdown Megapixel Image Performances 87                                    |

| 5.20 | Topdown Image Size Runtime Variations                                                  |

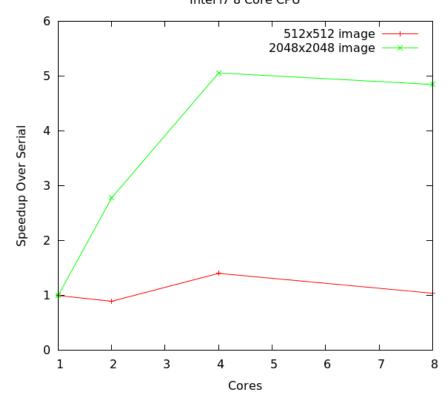

| 5.21 | Unregularised Topdown Per-Core Speedups                                                |

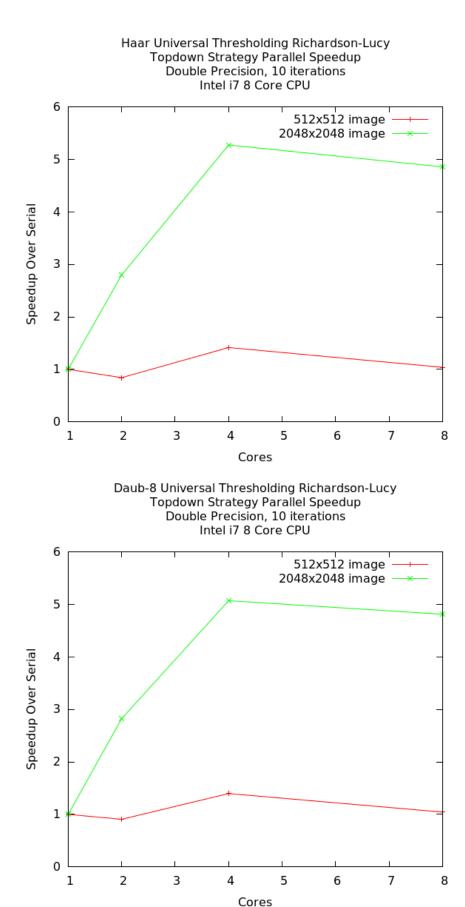

| 5.22 | Regularised Topdown Per-Core Speedups                                                  |

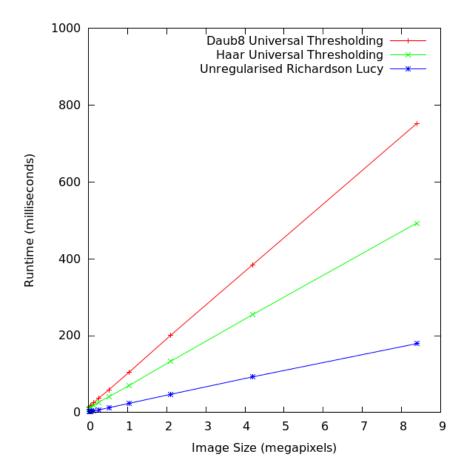

| 5.23 | Unregularised Streaming Megapixel Image Performance 92                                 |

| 5.24 | Regularised Naive Megapixel Image Performance                                          |

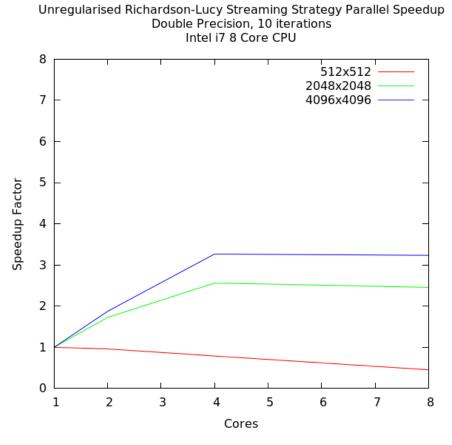

| 5.25 | Unregularised Streaming Per-Core Speedups                                              |

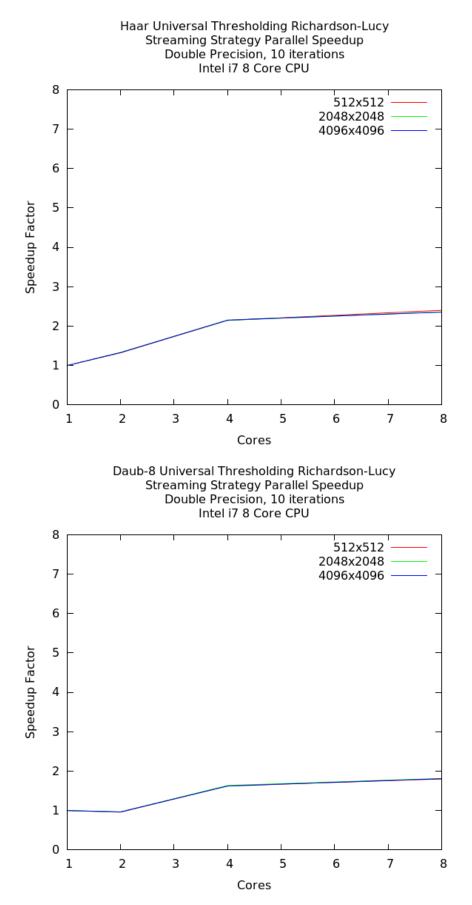

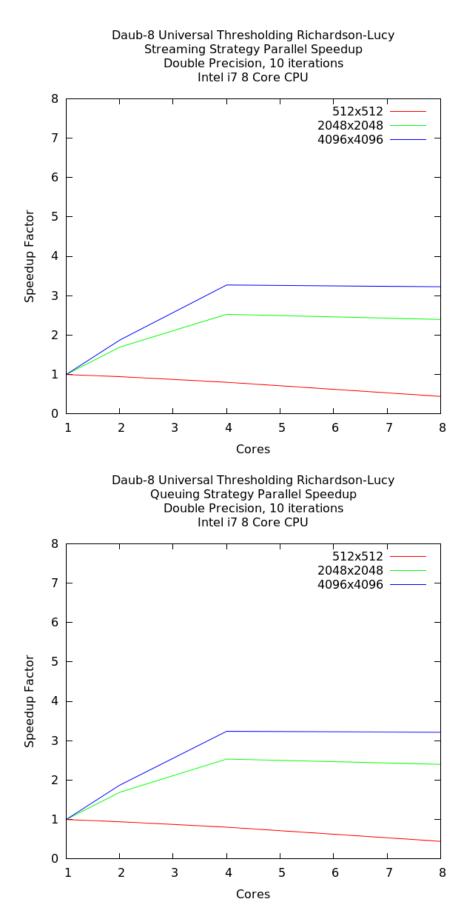

| 5.26 | Regularised Streaming Per-Core Speedups                                                |

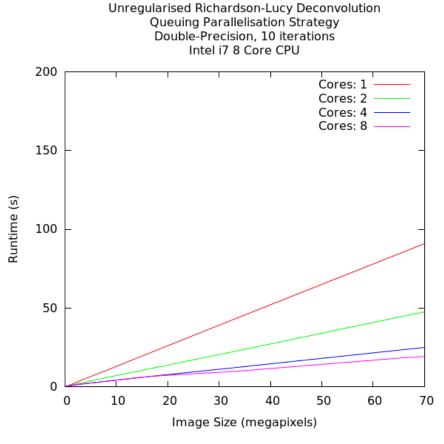

| 5.27 | Unregularised Queuing Megapixel Image Performance                                      |

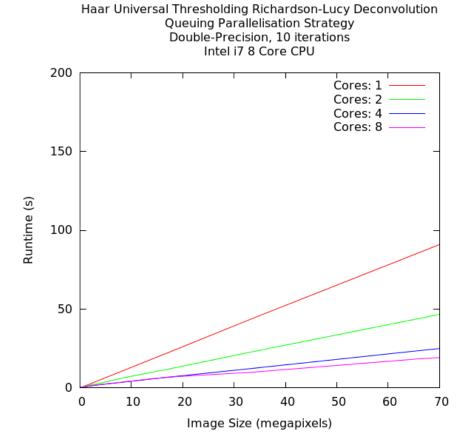

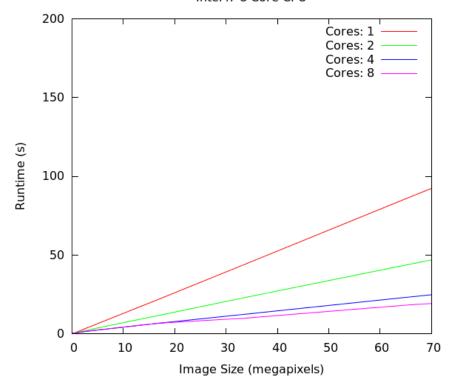

| 5.28 | Regularised Queuing Megapixel Image Performance                                        |

| 5.29 | Unregularised Queuing Per-Core Speedups                                                |

| 5.30 | Regularised Queuing Per-Core Speedups                                                  |

| 5.31 | GPU Naive Megapixel Image Performance                                                  |

| 5.32 | GPU Streaming Megapixel-Gigapixel Image Performance $\ \ldots \ \ldots \ \ldots \ 102$ |

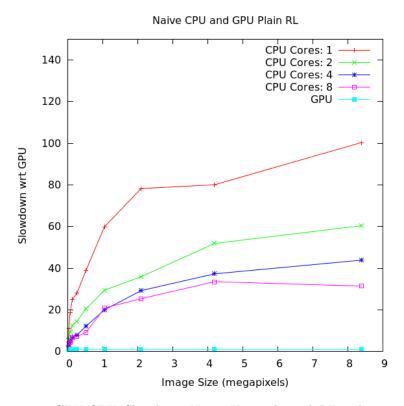

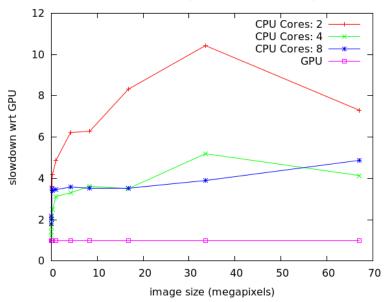

| 5.33 | GPU-CPU Slowdown Naive Unregularised RL                                                |

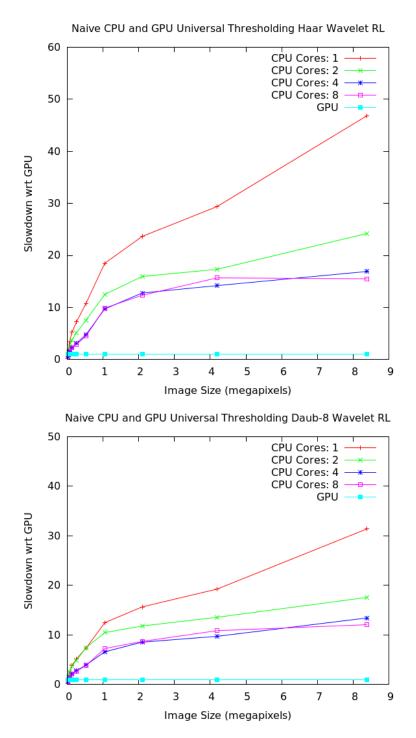

| 5.34 | GPU-CPU Slowdown Naive Universal Thresholding Haar & Daub-8 RL $$ . 104                |

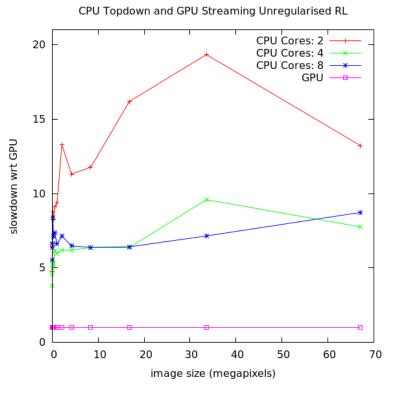

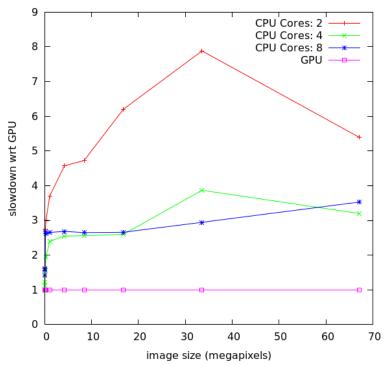

| 5.35 | GPU-CPU Slowdown Unregularised RL                                                      |

| 5.36 | GPU-CPU Slowdown Universal Thresholding Haar & Daub-8 RL 106                           |

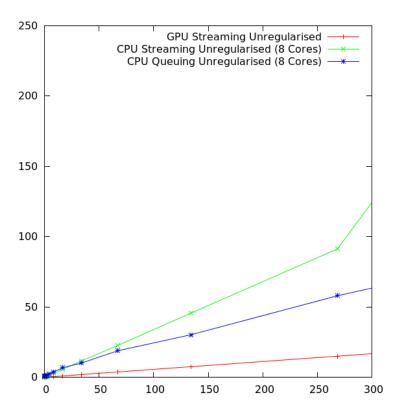

| 5.37 | GPU-CPU Unregularised 100 megapixel deconvolution 107                                  |

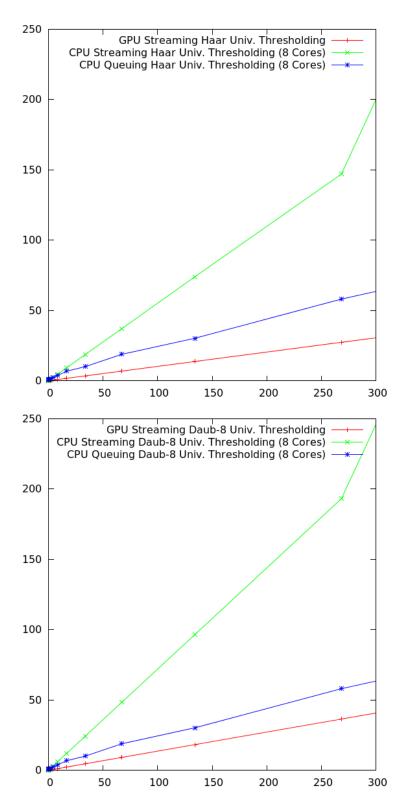

| 5.38 | GPU-CPU Regularised 100 megapixel deconvolution                                        |

| C 1  | 1                                                                                      |

| C.1  | 154                                                                                    |

# List of Tables

| 6.1 | Naive Plain Deconvolution, Line-Reference Counts                         | 118      |

|-----|--------------------------------------------------------------------------|----------|

| 6.2 | Naive Haar Universal Thresholding Deconvolution, Line-Reference Counts   | 118      |

| 6.3 | Naive Daub-8 Universal Thresholding Deconvolution, Line-Reference Counts | i<br>119 |

| 6.4 | Topdown Unregularised Deconvolution, Line-Reference Counts               | 122      |

| 6.5 | Topdown Haar Universal Thresholding Deconvolution, Line-Reference        |          |

|     | Counts                                                                   | 123      |

| 6.6 | Topdown Daub-8 Universal Thresholding Deconvolution, Line-Reference      |          |

|     | Counts                                                                   | 192      |

## Abstract

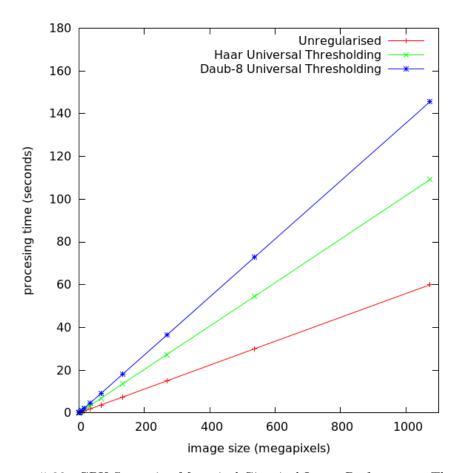

This thesis investigates the comparative performance of multicore CPU and general purpose GPU on a commodity desktop computer. To investigate this, an image deconvolution software package (IMPAIR) was updated from its original cluster-computing design to support both of these parallel architectures. The IMPAIR software was chosen for this investigation due to the high memory and computational demands of the image restoration algorithms it implements, coupled with these algorithms' natural amenity to highly parallelised solutions.

IMPAIR performs the image deconvolution operation by parallelising either the unregularised Richardson Lucy algorithm (RL) or a wavelet regularised variant of Richardson Lucy (WRL), which carries a significantly higher computational cost but is more robust to the presence of high levels of noise in the algorithm's input image. In order to support this WRL algorithm, general use wavelet shrinking libraries were developed for both the GPU and CPU, where a  $\times 2$   $-\times 3$  speedup of the GPU wavelet shrinking to the CPU wavelet shrinking was achieved.

In total, eight parallelisation strategies for the IMPAIR deconvolution algorithms have been implemented and their runtime performance on a commodity desktop hardware is presented. Of the strategies presented, the "Topdown" multicore CPU strategy and the "Streaming" GPU strategy achieve similar runtimes, but the reduced memory footprint of the GPU Streaming strategy permits scaling up to image data over ten times the maximum capacity of the multicore CPU Topdown strategy, for both the regularised and unregularised Richardson Lucy algorithms.

## Acknowledgements

I am heavily in debt to the following people for the aid, advice, and infinite patience they made available to me over these last six years:

Firstly, my supervisor, Professor Shearer. He has pulled me back from starting down a winding path to nowhere and pointed me back in the direction I should be going more times than I can count. Thank you.

Secondly, Professor David Gregg and Doctor Ray Butler, who played the exhausting roles of external and internal examiner with a methodical patience and understanding I am in awe of. Thank you both.

Thirdly, the staff and postgrads of the Centre for Astronomy, NUI Galway, in particular for the inviting welcome offered to me by them in my first year, when I arrived a stranger to the department. Thank you all.

To those people with whom I have shared living space, be it an office, or a house, or corner of a sitting room. I've wrecked all their heads with my ramblings, and none have ever held it against me. To Catherine, Simon, Sean, Susan, Gillian, Diarmaid, Paul, Navtej, Ronan, Paul, Lisa, Eoin, Mags, Gordon, Eamon, Kieran, Nicola, Aisling, Chris, Hazem, Camile, Siobhán, James, Barry, Ben, Donal, John, Jimmy, Suzi, and many, many, many others: Thanks a million.

Finally, my parents, Mary and Tom, and my siblings, Peter and Clara. Thanks for bearing with me through this.

PS. Emergency thank-yous to Lisa, Laura, and Eoin for dropping everything to help me out when time was of the essence. Thanks!

# Declaration of Authorship

| 1, the Candidate, certify that the Thesis is an my own work and that I have not obtained |

|------------------------------------------------------------------------------------------|

| a degree in this University or elsewhere on the basis of any of this work.               |

|                                                                                          |

|                                                                                          |

|                                                                                          |

|                                                                                          |

|                                                                                          |

| Signed:                                                                                  |

| Michael Sherry                                                                           |

| Wilchael Shelly                                                                          |

|                                                                                          |

|                                                                                          |

| Date:                                                                                    |

|                                                                                          |

## Chapter 1

# Heterogeneous Computing on the Modern Desktop Computer

#### 1.1 Introduction

A modern Desktop PC is a vastly heterogeneous beast. The combination of CPU model and manufacturer, Operating System API, RAM caching properties and strategies, virtualisation environment, persistent storage facilities, and special purpose hardware on both the mother board and expansion ports varies greatly between machines. While writing software that will run on all of the various configurations that exist is possible, writing software that will take advantage of any relevant optimisations available requires direct intervention and design decisions on the part of the developer. Unfortunately there is both the danger and expectation that since these decisions require insight into the underlying working of the machines, any optimisations will result in source code that is neither clearly written from an application domain point of view, nor easily maintained or ported to other systems.

In particular, the wide variation in multicore CPU architectures currently in circulation, including dual core, quad core and hyperthreaded 8 core CPUs, as well as the older generation of single core CPUs, has made it increasingly difficult to write software that will run evenly across this variable landscape of hardware [1]. The move from serial, single core CPUs to multicore CPUs and the introduction of programmable GPU cards in the standard Desktop PC initially left popular compilers, their programming languages, and runtime environments unable to take advantage of hardware at their disposal, unlike the previous transition from scalar to superscalar CPUs for desktop computing, which provided a transparent boost in performance [2]. Though the situation has gradually improved with the introduction of cross platform library suites compatible and tuned to

wider ranges of these architectures [3][4][5], taking on the responsibility of managing the hardware resources manually or limiting the portability of the software via a non-standard framework is not an attractive choice for a software developer.

However, an exciting consequence of this fundamental shift in the make up of the common Desktop PC is a further closing of the gap between High Performance Computing platforms and the ubiquitous Desktop PC platform. Already this has allowed for a more seamless migration of software in both directions between these two domains, in a much more straightforward manner than previous generations of hardware were able to permit. Since the Desktop PC can be considered a physical miniaturisation of a computational cluster [6], Desktop software (provided it correctly exploits this miniaturised HPC architecture) can now scale up satisfactorily in terms of both throughput and latency when deployed on a modern HPC node or cluster without any source code modifications. Similarly, HPC software can be expected to scale downward gracefully to the Desktop PC.

#### 1.2 Concurrency and Parallelism

Early advances in parallelism found success in the automatic parallelisation of serial software to better make use of the ability of the internal functional units of a CPU to operate in parallel. This automatic parallelisation of CPU instructions was achieved at the compiler level, where the compiler statically scheduled multiple functional units to operate simultaneously; and at the CPU level, where the CPU dynamically scheduled multiple functional units to operate simultaneously in the hope that this would better parallelise software with more non-deterministic control flow. As a data-processing application spends a disproportionately large amount of its runtime within looping structures, emphasis was put on parallelising the sequences of instructions if they are within a loop, and on simultaneously executing the instructions from successive iterations of a loop if the iterations are found to be safely re-orderable [7]. By the end of the 20<sup>th</sup> century, the limits of automatic parallelisation at the instruction-level had been reached [2].

Significant research into the behaviour of parallel computers began in the 1960s with the introduction of the overlapped fetch-decode-exec cycle CPU design [8] and array-processor machines [9][10], and during this period a simple model of parallel computing now known as the Flynn taxonomy [11] was put forward. Unlike the more theoretical models of parallel computing (such as Hoare's Communicating-Sequential-Processes [12], Hewitt's Actor Model [13], and numerous others [14][15]), which aim to cover all manner of forms of concurrent and distributed algorithms, this model was developed only to

address the implementation of parallel execution in a single centralised processor, by covering the range of all possible configurations of the externally presented interfaces.

#### 1.3 The Flynn Taxonomy

The Flynn taxonomy [11] divides all forms of computational systems into four basic categories. These describe the interfaces, rather than the implementations, of service-like systems. Consequently, the taxonomy can be applied generally to any computational system—whether purely hardware, purely software, or any combination of the two—by treating the system as a black-box virtual machine, and identifying its place in the taxonomy based on the interface the virtual machine provides. This allows the taxonomy to sensibly categorise systems that are physically parallel, logically parallel (but physically serial), and systems that exhibit various combinations of both of these traits without having to take these details into account. Similarly, distinctions between shared and distributed memory address space systems, or hierarchical or otherwise non-uniform memory architectures, do not require special consideration under this taxonomy.

The four categories of the Flynn taxonomy are: Single Instruction Stream, Single Data Stream (SISD); Single Instruction Stream, Multiple Data Streams (SIMD); Multiple Instruction Streams, Single Data Stream (MISD); Multiple Instruction Streams, Multiple Data Streams (MIMD).

#### Single Instruction Stream, Single Data Stream (SISD)

The SISD interface describes the classic Von Neumann architecture (where the incoming instruction stream and data stream are logically separate, but travel from the same external store over the same transfer bus), and the Harvard architecture (where the incoming instruction stream and data stream are physically separated, traveling from distinct external stores over distinct buses). Processors with separate  $L_1$  instruction-cache and data-cache spaces, but combined  $L_2$ - $L_L$  caches similarly present an SISD.

A system that exposes an SISD interface can be trivially built on an underlying SIMD system by only utilising one of the SIMD system's data streams, and its only instruction stream. This is the standard approach in GPU, multicore, and cluster computing to perform the inherently serial operations that result in the bottlenecks for Amdahl's law [16]. In situations such as this, there is no performance benefit from building an SISD system on top of an SIMD system.

Examples Systems:

Figure 1.1

- Scalar Processors

- Pipelined Scalar Processors [8]

(present an SISD interface, though execution is parallelised by overlapping)

- Superscalar Processors [17]

(present an SISD interface, though execution is parallelised by overlapping and dependency tracking)

SISD over MISD is far more common, as this configuration describes the pipelined or overlapped fetch-exec cycle that has been available in CPUs for decades. Taking advantage of pipelined parallelism in this fashion to process a single datastream occurs frequently in software as a pattern to address IO limited problems.

SISD over MIMD can be achieved in either a similar fashion to SISD/SIMD (by only utilising one of the many instruction stream-data stream pairs), or by means of a global synchronisation lock between all the instruction streams, so only one instruction stream is ever progressing at any one time. A system constructed in this fashion is capable of out-of-order execution of the elements of the instruction stream, and complex branch prediction operations—though with comparatively less of a speedup than that which is introduced by instruction pipelining.

#### Single Instruction Stream, Multiple Data Streams (SIMD)

The SIMD interface describes a system that processes a set of parallel data streams according to the same instruction stream. It is defined as a set of parallel data streams that pass through the CPU, controlled by only one instruction stream. A sufficiently large SIMD processor is capable of operating on N arguments in the length of time that an SISD processor can operate on 1, giving an average latency of less than the length of

Figure 1.2

time it takes to process an instruction on an SISD machine. It appears as if the first instruction was delayed, but the successive instructions were performed instantly.

#### Example Systems:

- Array Processors [9][10]

- Vector Processors [18][19]

- Array Languages [20][21]

- Map-Reduce Frameworks [22]

The SIMD interface is often implemented over SISD systems due to the concise description this interface affords for operations on collections of data [20]. The popular map and reduce operations of functional and big data programming languages are both SIMD operations, as are the element-by-element vector operations of Matlab, Octave and Python that remove the need for the programmer to explicitly loop through collection data in order to perform primitive arithmetic operations. Similarly, CPU SIMD register operations can be executed using scalar functional units operating without the delay of decoding N instructions for each of the N arguments [19].

SIMD/MIMD is achieved by duplicating the instruction stream so it is passed with each data stream. This method is the fundamental technique behind massively multicore and cluster computing software, where concurrent hardware is utilised in a deterministic fashion.

#### Multiple Instruction Streams, Single Data Stream (MISD)

The MISD interface describes a system that processes a single data stream according to a set of parallel instruction streams. It is the Flynn taxonomy category that shares

Figure 1.3

much in common with data-flow programming, stream processing, neural-network-like hardware and software and, in particular, hardware and software pipelines of IO limited processing systems, as this approach hides the latency of processing large batches of data by staggering the output instead of delivering it in one go.

While MISD hardware typically underlies all single core CPUs and their SIMD register operations, MISD pipelines occur throughout the software stack in order to hide the latency or increase the responsiveness of IO limited processes. A classic example is the shell pipeline on multitasking OS: data streamed from a single source (typically an IO bottleneck) is processed by a set of SISD applications running in parallel—MISD/MIMD—allowing disk IO and computation to be performed in parallel, without any explicit requests or the complications involved in asynchronous communications.

#### Example Systems:

#### • Dataflow Processors [23]

(where each datum is (potentially) associated with many instructions, and is evaluated as soon as the arguments are available. Dataflow processors also exhibit MIMD behaviour, depending on the nature of the associations.)

#### • Neural Network Processes and Processors [24]

(where each datum is 'fanned-out' to many nodes in the network, which correspond to instructions.)

# Multiple Instruction Streams, Multiple Data Streams (MIMD) Examples:

#### • Very-Long-Instruction-Word Processors [25]

(Where multiple instructions are explicitly requested to be performed simultaneously. This is MIMD at the Instruction-Level.)

#### • Dataflow Processors [23]

(Where multiple instructions are implicitly requested to be performed simultaneously, due to the "independence of their dependencies." This is MIMD at the Instruction-Level, though dataflow processors also exhibit MISD behaviour.)

#### • Reduction Processors [26]

(Lazily-Evaluated Dataflow processors. No or low-priority speculative execution [27]. Each instruction is processed once its result is required by an executing instruction.)

#### • Temporal Multithreading Processors [11]

(Where multiple data-instruction stream pairs are performed in an overlapping fashion. This is MIMD at the Thread-Level.)

#### • Simultaneous Multithreading Processors [28]

(Where multiple data-instruction stream pairs are performed simultaneously. This is MIMD at the Thread-Level.)

#### • Multicore Processors [29]

(Where multiple SISD or MIMD processors operate on their own data-instruction stream pairs simultaneously. A miniaturisation of a Symmetric Multiprocessor Computer. This is MIMD at the Thread-Level.)

#### • Symmetric Multiprocessor Computers [2]

(Where multiple SISD or MIMD processors operate on their own data-instruction stream pairs simultaneously. A predecessor of Multicore Processors. This is MIMD at the Thread-Level.)

#### • Cluster Computers [30]

(Where multiple SISD or MIMD processors operate on their own data-instruction stream pairs simultaneously. A magnification of a Symmetric Multiprocessor Computer. This is MIMD at the Thread-Level.)

#### • Cloud Computing Infrastructure [31]

Figure 1.4

The MIMD model covers all distributed computing architectures, and corresponds to the more general concurrency based models of computation, including multicore architectures and network clusters, active threads and processes in a multitasking OS, and the Internet as a whole.

While MIMD hardware systems are typically implemented on top of sets of MIMD systems (networked multicore systems) or sets of SISD systems (the set of cores in a multicore CPU), the GPU architecture is constructed from an MIMD system built over a set of SIMD systems.

MIMD systems are advantageous in that they support an overlaid SIMD or MISD system without *needing* to internally serialise any parallel operations —and so without necessarily incurring any system slowdown.

#### Discussion

Since the Flynn taxonomy categorises parallel architectures based on a single aspect of their interface (the number of parallel streams), many of the internal mechanisms of parallelism that have been explored over the last 60–70 years of computer history appear indistinguishable from this point of view, or straddle multiple categories. For example, a processor that contains a single instruction stream, but internally contains multiple Arithmetic Logic Units or Multiple Floating Point Units that are capable of simultaneous operation on distinct registers, does not present as a parallel processor under the Flynn taxonomy. Similarly, a processor that contains several instruction and

data streams, but which internally is restricted to operating on no more than one pair of registers simultaneously, presents as a parallel processor under the Flynn Taxonomy.

Behind the instruction-stream/data-stream interface, a processor is composed of independent logic units and state registers, and an instruction-stream "interpreter", that engages or disengages the underlying logic units on specific registers. This "interpreter" can act on an abstract language, that dynamically assigns operations to unused logic units [32] and blocks processing until these logic units have completed [17], or on a concrete language, where every instruction is capable of controlling all internal logic units simultaneously, and the processor takes no action to prevent the same unit being engaged while it is still in process [25]. While the latter option allows for more expressive use of the inherently parallel components of the CPU, there are software development and deployment costs to such an architecture that limit its applicability [2].

An intermediate design between these two extremes is the dataflow processor [23]. This processor "interprets" a serialised dependency graph of instructions, rather than a stream, which is then evaluated by dynamically scheduling the independent logic units of the processor as they become available. As a consequence of this approach the begin-time and end-time of the operations described in the instruction stream are performed in an order that may bear no relation to the ordering in the serial representation of the dependency graph. Approaches put forward as hybrid Von-Neumann and dataflow architecture [33] attempted to take advantage of the scenarios where superscalar processors unexpectedly outperformed dataflow processors [34] due to reduced ('free') synchronisation costs, and where dataflow processors allowed for multithreading behaviour at a lesser cost than superscalar processors could provide. Commodity desktop computers like the Intel i7 family of processors avail of this functionality in a limited form, where a small, sliding window of the instruction stream is de-serialised into a dependency graph, and then executed out-of-order. The Intel processor logical threading approach is built on top of this mechanism, where the dependency graphs of the two logical-thread instruction streams are treated as a single graph, allowing for inter-thread dependencies to exist and be performed meaningfully, while also allowing for operations in the two threads to be performed without any interdependent operations within the execution window.

Speculative execution is another approach to parallelism that is difficult view in terms of the interfaces of the Flynn taxonomy. For speculative execution, not only are the register operations performed in a different ordering to how they appeared in the serialised form of the dependency graph, but also out-of-order to how they should be performed when evaluating the dependency graph. This is possible for subgraphs of conditional expressions that do not internally make use of the value that lead to the conditional branch. In these situations, portions of the consequences of both outcomes of the branch

can be executed before the value of the condition is known, and one set of consequences discarded once the condition has been evaluated. Like logical hyperthreading, this behaviour falls out naturally from the construction of a dependency graph from the instruction stream of the processor. In best-case circumstances the consequences of both outcomes of the branch can be evaluated simultaneously, as there will necessarily be no further inter-dependencies between their sub-graphs, and sufficient computational units that the operations of both subgraphs can be scheduled simultaneously.

Parallel cache hierarchies that feed parallel cores do not feature in any way in the Flynn taxonomy, since they appear as either external to the incoming datastreams to an SIMD processor, or as slower internal registers available to an MIMD processor.

The modern commodity desktop computer contains elements of parallelism inherited from pipelined processors [8], superscalar processors [17], streaming and vector processors [35][36], dataflow processors [23], simultaneous multithreading [28] and temporal multitasking processors [11], as well as being a miniaturisation of symmetric or homogeneous multiprocessor machines [2]. Various other parallel architectures exist, such as heterogeneous system-on-a-chip processors [37], dynamically reconfigurable Field Programmable Gate Array (FPGA) processors [38], and memristor based computation-in-memory decentralised computers [39], and the introduction of these new paradigms are expected to be the next necessary step in overcoming declining Moore's Law behaviour of each new generation of the commodity desktop computer.

#### 1.4 Parallelism in the Modern Desktop Computer

The modern desktop computer is composed of a hierarchy of parallel systems of various forms—some special purpose, some general purpose, some logically parallel, some physically parallel—and realising the benefits of each component requires an overview of the depth and extent of this hierarchy.

At the topmost level, the desktop computer is a single node in a vast MIMD networked system: the Internet. This provides the grossest level of parallelism that is leveraged by the computational cluster [30]. Latencies at this scale are high, and bandwidth is both limited and frequently severely non-deterministic—a factor which has driven the development of such tools as the Hadoop framework [22][40][6] as an approach to managing this complexity.

Within the box, so to speak, there are four main components capable of performing independent tasks, interacting via Direct Memory Access (DMA) regions of a shared volatile store. These are the CPU chips, the GPU devices, the network interface, and

the persistent storage system. The independent operation of these devices—two general purpose, two special purpose—is sufficient to provide high level MISD parallelism for the system as a whole.

Both the persistent and volatile stores avail of batch SIMD parallelism, at the scale of RAID devices [41], the internal hard disk platters, and the movement of data in fixed sized lines between RAM and cache, though as these are single or special purpose devices, this overview will not cover them further.

Both the multicore CPU chip and GPU device follow a similar, converging internal structure, with slight variations to tune their performance in favour of one use case over another, as is described below.

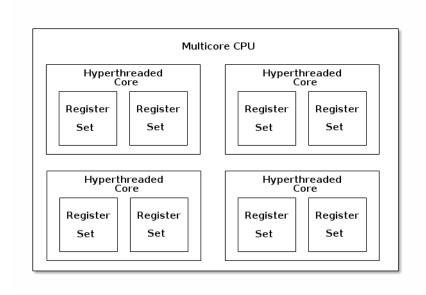

#### Multicore CPU

#### **CPU Core**

The CPU core contains the arithmetic logic units (ALU), floating point units (FPU), and embedded vector co-processor units, known as SIMD streaming extensions (SSE) on Intel CPUs. These three units are capable of operating independently of one another, allowing parallel operations to take place on separate CPU registers.

#### **GPU**

The GPU has a similar structure to the multicore CPU, but with different terminology for equivalent functionality [42].

Figure 1.5

The GPU equivalent of the per-core SIMD CPU vector unit is known as a warp. A warp provides conceptual lock-step SIMD execution of 32 threads. In current implementations, each 16 thread 'half-warp' is executed in lock-step, and each half-warp is executed in sequence, but this behaviour is not fixed in Nvidia's GPU road map, and reliance on this behaviour is discouraged as it may cease to hold for future GPU devices.

A set of warps is known as a block, and is equivalent to a set of hyperthreaded cores in a multicore CPU. A number of warps running in parallel within a block are implicitly synchronised at the beginning and end of a GPU routine, known as a *kernel*, but can also explicitly synchronise with one another during runtime.

At the coarsest level, a set of blocks running in parallel is known as a *grid*—which can be considered to be equivalent to either the physical cores in a multicore CPU, or a set of multicore CPUs running in parallel. A grid has the coarsest level of synchronisation, which only occurs at the beginning and end of a kernel's execution. There is no mechanism for explicitly synchronising blocks in a grid during a kernel's runtime, but since the blocks in a grid are synchronised at the end of a kernel's execution, constructing a grid-wide kernel as a pair of *before* and *after* kernels that are invoked in sequence allows for a grid-wide synchronisation to occur mid-way through the grid-wide kernel.

#### 1.5 Synchronisation & Lockstep Execution

Parallel systems built over more general concurrent systems (whether physically as a network of independent nodes in a cluster, or conceptually like SIMD parallelism built over a threading framework) inherit a certain degree of non-deterministic behaviour from the underlying concurrent machinery. In such systems it is necessary to have a concept of synchronisation, which specifies single points where the state of the parallel system is guaranteed to be predictable, even though between these synchronisation points the state may be unpredictable. At the software-level, synchronisation points can be explicit (via a command called by each thread), or implicit—which usually occurs when a program switches from one organisation of parallel threads to another.

The use of synchronisation points hides the underlying reliance on thread semaphores, shared and mutex locks, or Compare-And-Swap style atomic transactions at the thread-level, and memory-barrier superscalar processor operations at the instruction-level.

With this concept in mind, parallel systems like the per core SIMD vector registers can be thought of as parallel systems that synchronise after each operation—this can be thought of as progressing in *lockstep*. Conversely, CPU thread or GPU block based

multicore CPU or GPU SIMD software can be considered to move in lockstep at the resolution of the synchronisation points, rather than each operation.

#### 1.6 Parallel Speedup

Amdahl's Law [16] and Gustafson's Law [43] are two principles that describe how parallelism can improve the runtime of a parallel program. These rules deal separately with either improving the runtime by reducing the latency of the inner operations of a program, or by increasing the throughput or bandwidth of the inner operations.

#### Parallel Limits- Amdahl's Law

$$Speedup = \frac{1}{1 - f + \frac{f}{P}} \tag{1.1}$$

#### where

f = fraction of program that is parallelisable P = number of available processors

Amdahl's law gives the limit to the speedup the same program can exhibit when run on any number of cores. It is concerned with applications that wish to avail of parallel speedup to reduce the system's latency by as much as possible. Systems subject to Amdahl's Law initially receive a boost in speed as new cores are provided, but soon hit a point of diminishing returns where adding subsequent cores provides less and less of a speedup, until the runtime cannot be reduced to less than a base constant. This constant is the runtime of the inherently serial portions of the program—such as synchronisation points, initialisation procedures, or IO operations that cannot be parallelised. The proportion of time spent during these necessarily serial portions compared to the time spent in parallelisable portions is the maximum speedup that the software can achieve through parallelisation.

Amdahl's Law is formulated for processing datasets of a fixed size, and can be used to determine what fraction of a system's computational resources should be allocated to the program in order to get the best gains from their use [44]. When viewed in this fashion, it is used for determining what the optimal core-to-data ratio should be when designing a system that takes advantage of the behaviour characterised by Gustafson's Law.

#### Parallel Speed-up- Gustafson's Law

$$ScaledSpeedup = P + (1 - P) \times (1 - f)$$

(1.2)

#### where

f = the fraction of the program that is parallelisable P = the number of processors

Gustafson's Law applies to achieving parallel speedup by increasing the system's bandwidth by adding more nodes to a cluster, or memory and cores to software running on a multicore system. While this approach does not actually increase the speed at which the individual data are processed, it allows more data to be processed in the same period of time.

Gustafson's Law provides a mechanism for avoiding the point of diminishing returns predicted by Amdahl's Law, since in many parallel algorithms the inherently serial bottlenecks that dominate Amdahl's Law are of a fixed cost, that is neither proportional to the size of the dataset being processed, nor the number of processors being employed. In these cases Amdahl's point of diminishing returns is unreachable, as the software will always be spending a larger proportion of its time processing the data rather than performing synchronisation or initialisation operations.

Gustafson's Law is the primary justification for GPU based computing and Cloud Computing, where a reasonable runtime time is achieved by acquiring a suitable number of cores to process the dataset, rather than tuning the software to make maximum use of the cores at hand.

#### 1.7 Parallel Slowdown

Parallel slowdown manifests as an inverse form of Gustafson's Law, where as more cores are made available to the software, the overall throughput of the software decreases, until the runtime is slower than the same software running with less cores. This behaviour is due to the underlying behaviour of the hardware, or conflict with the wider ecosystem of OS daemons, services, and background user processes, rather than an error in the algorithm or implementation.

The most common cause of parallel slowdown for a multicore or GPU system is due to the behaviour of the memory hierarchy hidden behind the flat virtual memory model that is exposed to the programmer. The two primary forms this takes are thrashing—which is a well known issue in serial software as well as parallel software; and cache contention—which only occurs in parallel or concurrent systems [45][46].

#### Thrashing the Cache

The cache hierarchy that exists between the CPU and RAM is an attempt to smooth out the growing disparity between CPU speed and RAM speed. Unlike in the GPU, where transporting data up and down through the memory hierarchy must be done manually, CPU caching is an entirely hidden and automatic process, which uses a set of hardwired heuristics known as eviction strategies to determine how and when data should be pulled from RAM into the cache, or pushed from the cache back to RAM.

A fully-associate cache works analogously to virtual memory demand-paging, where an initial reference to a cache line replaces the least-recently-used (or some other heuristic) line of the cache with the newly referenced line, and subsequent references operate on the cached line in this location.

Cache thrashing is a similar problem to the hard disk thrashing that occurs when a program uses more virtual memory than there is physical memory available, and spends the bulk of its runtime copying data from the hard disk to ram and back to the hard disk. As the RAM size of computers grew since the initial introduction of virtual memory, this problem became less and less apparent, but it has since resurfaced due to the widening gap between RAM speed and CPU cache speed.

In both single core and multicore CPUs this behaviour occurs when the program operates on a larger region of main memory than can fit inside the CPU cache. The most straight forward approach to dealing with this problem is to re-organise the algorithm so it only operates on short contiguous chunks of main memory at a time. This memory access pattern can be easily accommodated by the current caching strategies employed in hardware. Due to the drastic difference in IO speed between the cache and RAM, algorithms can afford a significant amount of computational overhead in order to achieve this new memory access pattern, while still improving runtime over an unoptimised version.

For multicore CPUs there is a further complication in that the cache-to-core ratio is not constant between different CPU models. Some models have a completely unique set of level 1, level 2, and level 3 caches for each core, some hyperthreaded multicore CPUs shared the same level 1 cache between each pair of logical processors, and some models share the level 3 cache between all cores. This causes problems in two circumstances:

- 1. Multicore CPU software developed for one CPU model is run on a different model that shares cache between cores.

- 2. Scaling the software from a small number of CPU cores to all CPU cores. If the cache was already fully occupied for  $\frac{N}{2}$  cores, scaling out to N cores will result in a

dramatic slowdown with a lower throughput per core ratio than the less parallelised version.

This situation can occur for multicore CPU programs, even if the algorithm has been modified to operate on chunks of RAM, if the chunks are too large. This problem can be avoided by either configuring the software with a different chunk size for each CPU model it is run on, or by choosing an arbitrarily small chunk size, that is guaranteed to fit several times over into a core's cache, whether it is shared or not.

#### **Cache Contention**

Cache contention is the term used to describe the effect of multiple threads of execution attempting to fully utilise the available cache [46][45]. This phenomenon occurs in situations where multiple processes or threads are sharing at least one level of the same intermediate memory hierarchy. For SIMD multithreaded software, it can be managed by constraining each thread of the software to only make use of  $\frac{1}{N}^{th}$  of the available cache space. Managing the situation in cases of MIMD software is more involved, as the rate at which cache lines are re-used can result in threads over-utilising or under-utilising the cache, based on the relative rates at which they reference their respective memories, rather than their individual memory access patterns.

#### 1.8 This Work

This thesis presents an investigation into the effectiveness of two related mechanisms of parallel computation that are readily available on a commodity personal computer: Multicore CPU hardware and general purpose GPU hardware. The aim of this thesis is to address the question of what computational tasks are the generic CPU and GPU processor types more suited for, in the context of desktop scientific computing. This investigation is conducted by means of an exemplar image processing package, IMPAIR, which presents a set of parallelised image processing algorithms. The performances of this set of image processing algorithms are evaluated in terms of their total running times, resource requirements, scalability, and to what extent the strategies are in a position to address the medical and astronomical imaging specific problems of achieving gigapixel deconvolution, realtime deconvolution, and kilopixel-to-megapixel blind deconvolution in a practical fashion on a commodity desktop computer.

The implementation of these algorithms attempts to take advantage of the presence of the independent physical cores, the shared logical cores, and the floating point vector registers of the Multicore CPU, and the similar structures found in the GPU architecture, referred to as blocks, warps, and half-warps respectively in the CUDA language specification. The effectiveness of this attempt is discussed in detail in Chapter 6, particularly with respect to the scalability of the strategies for the CPU implementations, where the runtime performance is subject to worst-case interaction with the memory hierarchy.

This evaluation found that the GPU Naive strategy is capable of 24 frames per second unregularised deconvolution of a 1 megapixel ( $1024 \times 1024$  pixel) image, and 24 frames per second wavelet regularised deconvolution for a 200 kilopixel ( $512 \times 512$  pixel) image, while the CPU Naive strategy achieved 24 frames per second deconvolution for 60 kilopixel ( $256 \times 256$  pixel) images.

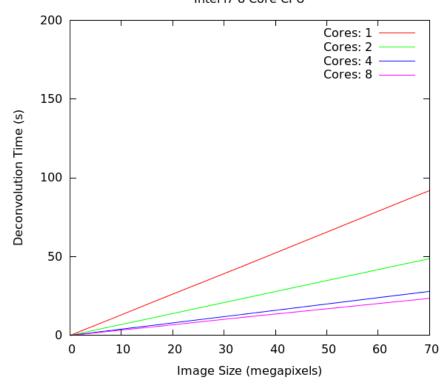

The GPU streaming strategy was found to be capable of deconvolving gigapixel images at a rate of less than 15 seconds per iteration for the wavelet regularised algorithm, and 6 seconds per iteration for the unregularised algorithm.

The larger memory requirements of the CPU Topdown strategy are an obstacle to scaling to the gigapixel range, but for images in the megapixel range the CPU Topdown strategy was found to perform within  $5 \times$  the speed of the fastest GPU strategy.

This thesis presents two parallelised implementations of the Wavelet-Regularised Richardson Lucy algorithm, suitable for spatially variant image deconvolution of gigapixel images on commodity desktop hardware and the realtime deconvolution of a confocal microscopy image acquisition stream. To the best of the author's knowledge, the GPU and Multicore CPU performance of this Wavelet-Regularised Richardson Lucy algorithm has not previously been investigated.

Through the implementation of the parallelised wavelet-transform algorithms, aspects of the results of the theoretically optimal discrete wavelet transform algorithm on the GPU presented by Song et al [47] have been tested; IMPAIR's implementation of the Song et al Block-Based DWT performs as well as IMPAIR's previous transpose-based DWT algorithm in all cases except for the GPU Streaming Strategy, where the Block-Based DWT out-performed the transpose-based DWT. As an exact re-implementation of the Block-Based DWT was not implemented by IMPAIR, future work will include a second comparison between these two approaches.

Based on the wavelet transform library, a parallelised wavelet-shrinking library has been developed for the GPU and CPU and its behaviour profiled.

The novel contributions of this work are the Multicore CPU and GPU implementations of the wavelet-regularised deconvolution algorithm, and the investigation of the performance of both these algorithms and the unregularised Richardson-Lucy deconvolution algorithm on the Multicore CPU and GPU. This investigation has laid the groundwork

for the future developement of a spatially variant wavelet regularised deconvolution image processing tool, and for the developement of a wavelet regularised blind deconvolution algorithm, which would have been impractical in practice without the underlying Multicore and GPU parallelisation.

The runtime performance of an earlier version of the regularised and unregularised CPU Naive and Topdown strategies, and an earlier version of the unregularised, and in-progress version of the regularised GPU Streaming strategy were presented at the SPIE Image Processing: Algorithms and Systems XI Conference in February 2013 [48].

The structure of this thesis is as follows:

Chapter 2 will present a broad overview of the field of computer vision, and its relationship to image restoration, concluding with an overview of the various approaches to solving the ill-posed inverse problem of image deconvolution.

Chapter 3 will detail the domain-specific opportunities for the parallelisation and optimisation of image processing primitives that are required by the image restoration algorithms discussed in Chapter 2.

Chapter 4 will present the development and testing of the parallel wavelet transform and wavelet shrinking libraries, using the techniques of Franco et al, van der Lann et al, and Song et al as described in the literature [49][47][50].

Chapter 5 will present the image restoration performance of the algorithms described in chapter 3, and the runtime performance benchmarks of the parallelisation strategies used in their implementation.

Chapter 6 will present an analysis of the results of two of these strategies in terms of the Multicore CPU algorithm's interaction with the Multicore CPU's cache-hierarchy.

Chapter 7 will then finish with an outline of the intended future developments for the software.

## Chapter 2

## Image Processing

#### 2.1 Introduction

As it stands, the modern desktop computer is a massively parallel machine, capable of processing large datasets via a hierarchy composed of coarse to fine grained parallel hardware with a corresponding memory hierarchy. Large scale image processing tasks are particularly responsive to parallel hardware [51] such as this, and are now within the grasp of a portable application software for a wide range of commodity hardware.

Tasks that have until recently required batch processing on small cluster computing frameworks, can now be comfortably performed interactively on large datasets, or even in realtime as the image dataset is acquired [52]—this enables general and transferable solutions to common image processing tasks to be employed across the board in desktop applications of computer vision.

# 2.2 Computer Vision, The Image Processing Pipeline & The Semantic Gap

This thesis is concerned with the development of parallelised deconvolution software for astronomical and medical imaging, as the deconvolution algorithm employed by the software has a history of use in these areas [53][54]. However, there are similar image and signal processing based domains that feature deconvolution problems, to which any deconvolution software might find application. For example, image deconvolution has been used in the areas of long range imaging, to restore images in the presence of atmospheric turbulence [55][56][57], motion blur caused by a hand shake during a hand-held camera's exposure [58][59], and the artificial deepening of the depth of field

of an image [60][61]. The interaction of a deconvolution process with other processes in the general domain of computer vision is beyond the scope of this thesis, but a brief description is presented here as an introductory section.

The term the semantic gap [62] is used to describe the discrepancy between the large amount of useful knowledge that is present in a digital image, and the small amount of domain specific knowledge that a software system presented with the image can process. The field of computer vision (CV) is the area of research devoted to closing, shrinking, or bridging this gap, and allowing software productive access to the vast, and exponentially increasing amount of digital image data that is currently acquired and archived by humanity.

Computer vision algorithms can be generally divided into two coarse categories [63]: those that slot into a stack of general purpose computer vision algorithms, producing image data to be viewed or processed by another algorithm; and those with a specific domain, that consume image data and produce non-image data (for example Optical-Character-Recognition algorithms), or associations between image data and non-image data that can direct domain specific image processing tasks (for example the iterative Optical Character Recognition image-preprossing approach described in [64]).

The approaches used in the solution of one domain-specific CV problem are at risk of being of little use to the solutions to similar problems in related domains, or of responding so differently to pre-processing steps as to render them counter-productive. For example, the pre-processing approach described in [64] relies upon the assumptions of the Optical Character Recognition of scanned and faxed documents, to the point that its applications to the classification of non-character images are not obvious or likely. However, the recent progress in the application of convolutional-neural-network software to such knowledge extraction problems [65] has found success in cases where techniques used in one domain-specific CV problem can be successfully repurposed and transfered to another [66].

A simplified version of the stack described in [63] is as follows:

- The optical system

- The acquisition system

- Image restoration processes

- Image segmentation processes

- Feature extraction processes

- Feature identification system

- Knowledge extraction system

where each element in the pipeline only interacts with its neighbouring elements in a feedforward manner (in the simplest case). The creation of a more expressive taxonomy of image analysis algorithms is described in [67] and [68]. The three central elements of this pipeline cover computational image processing related tasks, into which IMPAIR falls, while the first two hardware stages, and the final two information-system stages, are significantly different fields of study.

#### 2.3 Image Restoration

The image restoration process in the image processing pipeline aims to minimise the degradation that has occurred to the theoretical *true image* as it is processed and transformed through the optical and acquisition systems [63]. This degradation takes the form of blurring or warping of the true image by the optical system, and sampling errors—additive noise—introduced by the acquisition system.

Under certain conditions the observed image can be 'restored' to a spatial resolution that exceeds that of the acquisition [69]. These conditions are available to the restoration of astronomical images [70][71] (a star-field has a number of small foreground objects on a uniform background of values close to 0).

As it is an early process of the image processing pipeline, any improvements, whether in terms of runtime, reduced resource requirements, or restorative ability, will cascade onwards towards all processes that depend on its output [72][73][74][75], whether they be applied in the domains of realtime image processing, smartphone or embedded image processing, or the large scale mining of image datasets, like those found in medical imaging [76].

### 2.4 Metrics of Image Quality

For image restoration purposes, the two fundamental measurements of the degradation or quality of an image are the signal to noise ratio (SNR) of the image pixels, and the spatial resolution of the image. These aspects describe the behaviour of the sensor and optics of the acquisition system, respectively. The maximum spatial resolution that an image can represent is determined by the nature of the impulse response, or point-spread function (PSF), of the acquisition system. While an estimate of the SNR of the image data is not necessary for the application of the image restoration processes described in this chapter, an estimation of the acquisition system's PSF is required by the Richardson-Lucy [77][78][79] algorithms discussed in sections 2.8 and 2.11. This data can be obtained either from measurement, or derived analytically from a model of the image acquisition system [63].

The Modulation Transfer Function (MTF) is a representation of the quality of an imaging system, in terms of the dampening effect the system has on the amplitudes of its input spatial frequencies. The information displayed is in terms of the contrast between the light and dark regions of the image for the range of possible spatial frequencies, where a fully discernible spatial frequency will have a maximum contrast, and an unresolvable spatial frequency will have a contrast of zero.

#### 2.5 Denoising

Denoising signal data, or designing algorithms that are tolerant of the presence of noise in signal data, is an unavoidable problem for all computer vision applications [80][81]. Various techniques, linear and non-linear approaches, are employed to this end which range from spatial filtering and Wiener techniques to common Wavelet approaches [82][83][84][85][86]. Which of these is chosen will depend upon the computer-vision process, for example whether or not the additive noise in the input data is Gaussian distributed, and the requirements of the processes that will follow from the denoising step, for example whether or not photometry will be performed on the output data.

Denoising via crude global thresholding is most appropriate to signal data taken under highly controlled conditions, such as evenly illuminated printed text. More expressive variants of thresholding, where noise levels are reduced or shrunk, but not flattened, across the image have more general applications, and are more suited to adaptive methods, such as wavelet based denoising [87].

Linear filter based approaches perform denoising by convolving the signal with a filter designed to suppress variations in the image with a high spatial frequency. Depending on the choice of filter used—for example a Gaussian or box filter—this denoising approach can result in significant loss of contrast, and loss of spatial resolution in the signal. Consequently, these approaches are potentially counterproductive for image restoration processes that require a deconvolution operation to restore contrast or improve the spatial

resolution of the signal [88]. The behaviour of non-linear filters are more suitable for situations where features such as object edges must be preserved [89][90].

For an approach to generating iterative denoising algorithms from a 'black-box' denoising operation (in a similar fashion to the blind deconvolution algorithm discussed in 2.12), see [91].

Both thresholding and filter based approaches are dependent to some degree on the choice of specific parameters—either the threshold level, or the size and type of image filter. Adaptive approaches to denoising reduce or remove the need for such tunable parameters, removing the need for human supervision during the denoising process [92]. This behaviour is particularly desirable in situations where the denoising process is run frequently over a changing set of signal data where the same parameter value will not be applicable to each instance—for example, within an inner loop of an iterative image processing algorithm.

## 2.6 Deconvolution & The Deconvolution Problem

Deconvolution is the term given to the reversing or undoing the convolution of a signal with a kernel. It is an ill-posed inverse problem—meaning the deconvolution of a signal with respect to a kernel can only be estimated, as there is no guarantee of a unique nor stable solution [70].

The success of a deconvolution algorithm depends entirely on the properties of the kernel and the properties of the original signal. For certain input signals satisfactory deconvolution will not be possible, and likewise for certain convolution kernels. The clearest example of this is a low-pass filter kernel (like an averaging filter) that removes the presence of any high spatial frequencies in an image.

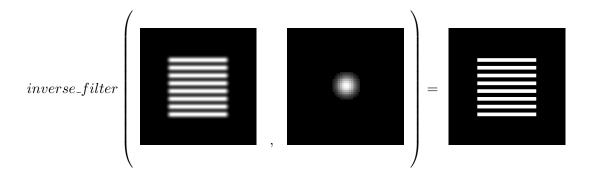

For signals and kernels with the appropriate properties, full reconstruction of the signal is possible via the deconvolution technique referred to as *inverse filtering* [63], or by Van Cittert deconvolution [93].

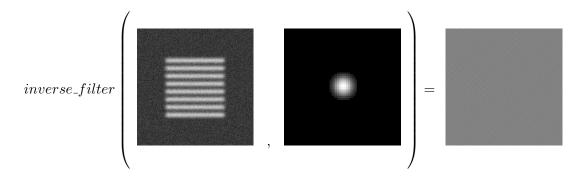

The deconvolution of images acquired by a detector system is complicated due to the presence of additive noise in the acquired image. This noise is amplified by inverse filtering or similar straight forward techniques for pure deconvolution. See Figure 2.2 for an example image.

Similarly, in a real world detector system any measurement of the PSF will contain imperfections, since it itself will be subject to additive noise and minor spatial variations. The problem of deconvolution for the purpose of image restoration suits algorithms that

Figure 2.1: IMPAIR Inverse Filtering Example Images. Examples of a 'perfect' inverse filtering operation performed by IMPAIR.

FIGURE 2.2: IMPAIR Inverse Filtering Noise Amplification Example Images. Extreme noise amplification via inverse-filtering a synthetic image with additive noise, showing the unsuitability of this technique for real world images which will contain some amount of unavoidable additive noise due to the nature of the acquisition system.

function acceptably with less than perfect knowledge of the PSF, and in the presence of varying levels of additive noise [70].

# 2.7 The Zoo of Deconvolution Algorithms

Deconvolution algorithms for image restoration range from a historical set of filter based approaches (such as image sharpening, unsharp masking, and the Wiener filter), to a broad and growing toolset of iterative algorithms [70].

Filter based approaches have the advantage of lower computational costs and memory requirements, and—due to their single-pass nature—more deterministic runtimes, making them well suited to problems of realtime image processing. Iterative methods, though more powerful, are more costly, and so historically found less use outside of special purpose hardware.

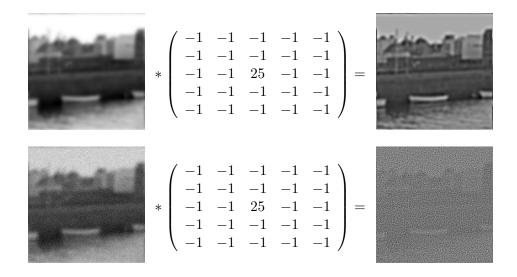

The typical filter based approaches to image restoration are:

Figure 2.3: Image sharpening with a  $3 \times 3$  pixel kernel.

Top: Sharpening of a low noise image.

Bottom: Sharpening of a high noise image. Noise amplification in restored image clearly visible.

Figure 2.4: Image sharpening with a  $5 \times 5$  pixel kernel.

Top: Sharpening of a low noise Image.

Bottom: Sharpening of a high-noise Image. Noise amplification in restored image clearly visible.

## **Image Sharpening**

This is the convolution of a filter designed to increase the contrast of the image over a small window (typically  $3 \times 3$  or  $5 \times 5$  pixel regions), and is prone to noise amplification.

#### **Inverse Filtering**

This is the algorithmic inverse of the convolution operation, defined in the Fourier domain as:

$$deconvolve(a,b) = \mathcal{F}^{-1}\left(\frac{\mathcal{F}(a)}{\mathcal{F}(b)}\right)$$

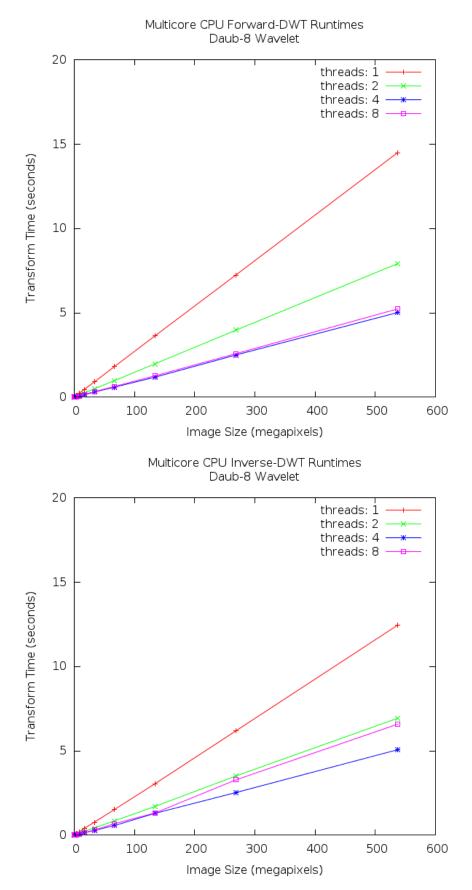

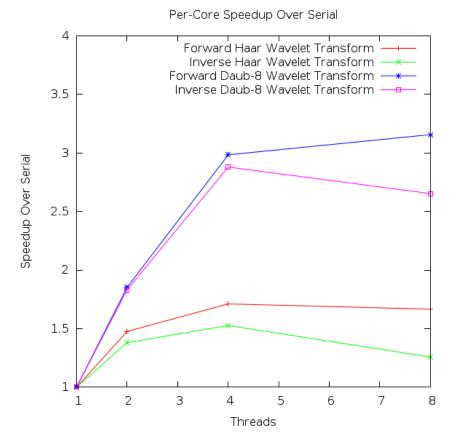

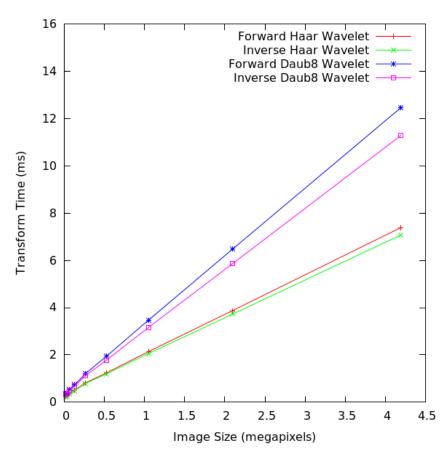

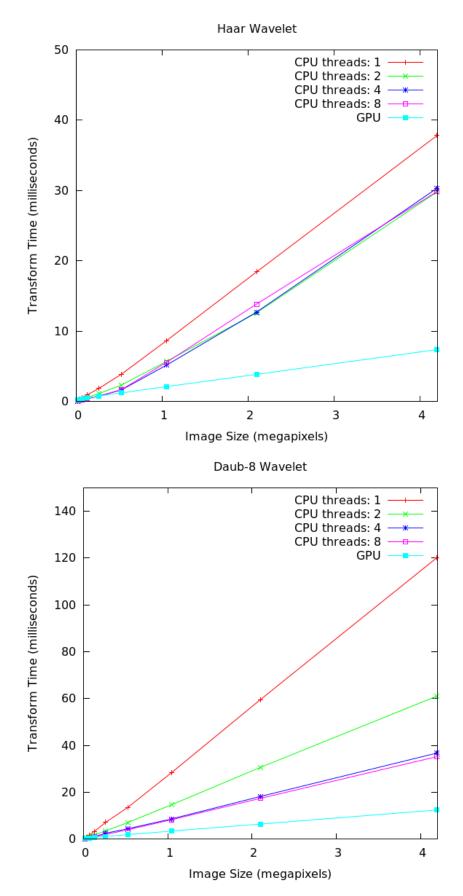

(2.1)